### MMC CAPACITOR VOLTAGE BALANCING IN NEAREST LEVEL CONTROL

Mattia Ricco

Aalborg University, Energy Technology Department, Pontoppidanstæde 111, 9000 Aalborg, Denmark

#### Introduction

Sorting Methods for NLCProposed Solutions:

- Sorting Networks

- Capacitor Voltage Mapping Strategy

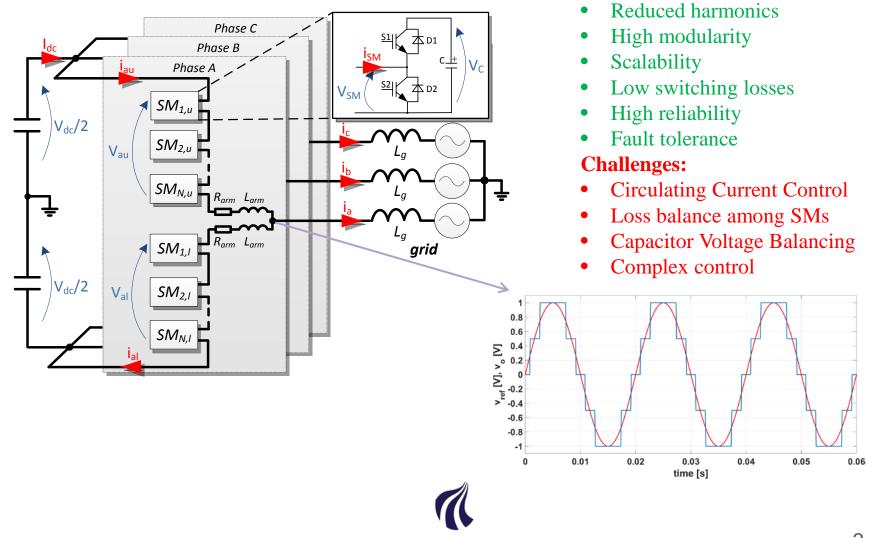

## **Structure of MMC**

**Advantages:**

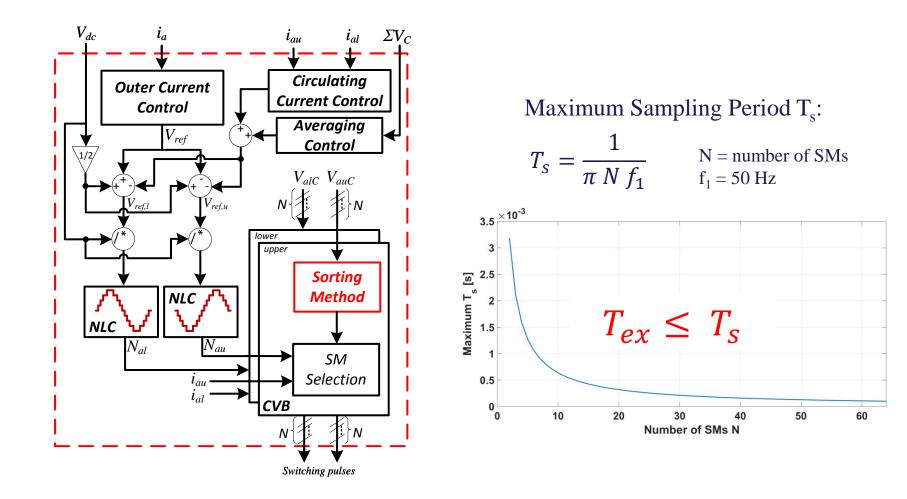

### **Control scheme of MMC**

#### >Introduction

### Sorting Methods for NLC

Proposed Solutions:

- Sorting Networks

- Capacitor Voltage Mapping Strategy

## **Sorting Methods for NLC**

#### **Bubble Sorting Algorithm**

#### Advantage:

• Easy to implement.

#### **Drawbacks:**

- The execution time is not fixed and it depends on the input list.

- The execution time increases when N grows.

#### Max/Min Approach

#### Advantage:

- Easy to implement.

- The sorting method is avoided.

- Less execution time than Bubble sorting algorithm.

#### **Drawbacks:**

• If more than one SM has to be inserted, for example during faults, the max/min method needs more sampling periods to insert the required SMs. This affects the control dynamic.

## **Sorting Methods for NLC**

#### **Tolerance Band**

#### Advantage:

• Reduced switching frequency.

#### **Drawbacks:**

• A sorting method is required.

#### >Introduction

Sorting Methods for NLC

### Proposed Solutions:

- Sorting Networks

- Capacitor Voltage Mapping Strategy

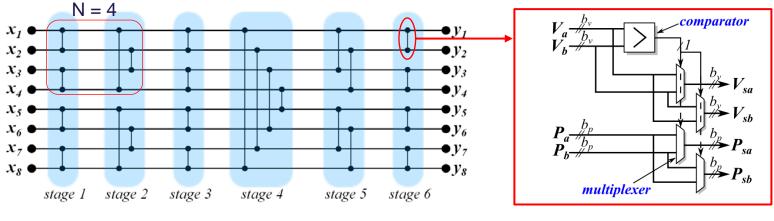

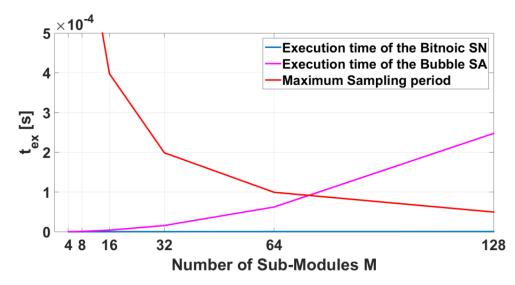

## **Sorting Networks**

- The Sorting Networks are typically good solutions for FPGA:

- Even-Odd Sorting Network

- **o Bitonic Sorting Network**

- They are faster than the sorting algorithms due to the parallel construction.

Bitonic Sorting Networks with N = 8

Compare & Swap Operator

M. Ricco, L. Mathe and R. Teodorescu, "FPGA-based implementation of sorting networks in MMC applications," 2016 18th European Conference on Power Electronics and Applications (EPE'16 ECCE Europe), Karlsruhe, 2016, pp. 1-10.

## **Sorting Networks**

- The Sorting Networks are typically good solutions for FPGA:

- Even-Odd Sorting Network

- **o Bitonic Sorting Network**

- They are faster than the sorting algorithms due to the parallel construction.

M. Ricco, L. Mathe and R. Teodorescu, "FPGA-based implementation of sorting networks in MMC applications," 2016 18th European Conference on Power Electronics and Applications (EPE'16 ECCE Europe), Karlsruhe, 2016, pp. 1-10.

#### >Introduction

Sorting Methods for NLC

#### Proposed Solutions:

Sorting Networks

Capacitor Voltage Mapping Strategy

Conclusions

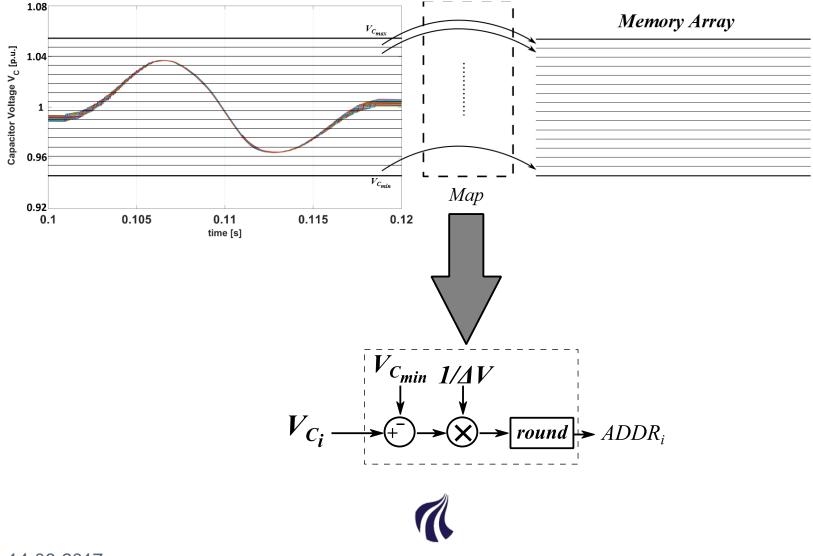

M. Ricco, L. Mathe and R. Teodorescu, "New MMC capacitor voltage balancing using sorting-less strategy in nearest level control," 2016 IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, 2016, pp. 1-8.

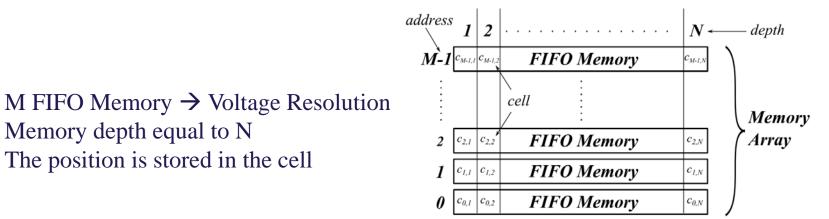

Memory depth equal to N

The position is stored in the cell

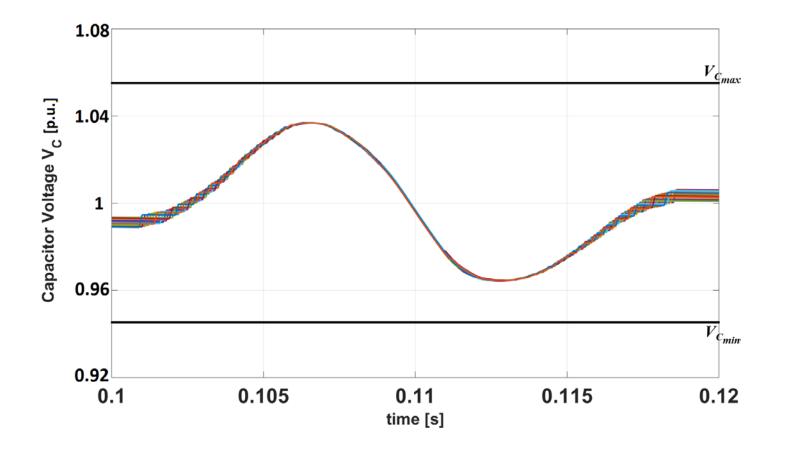

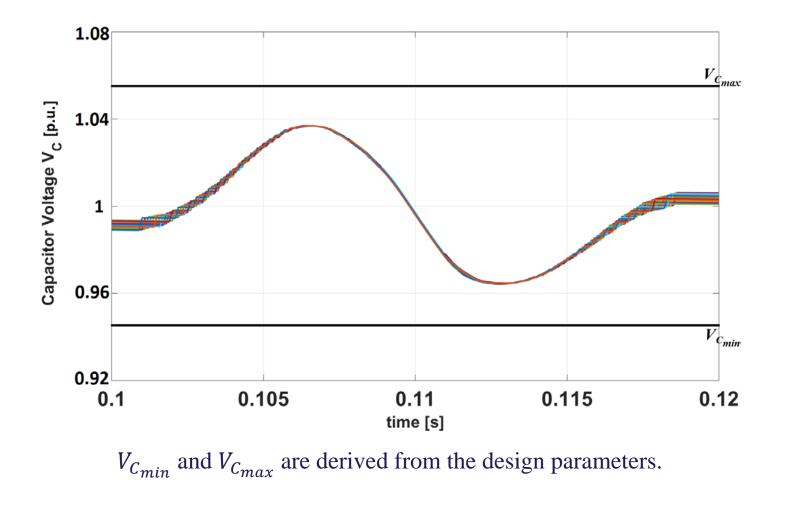

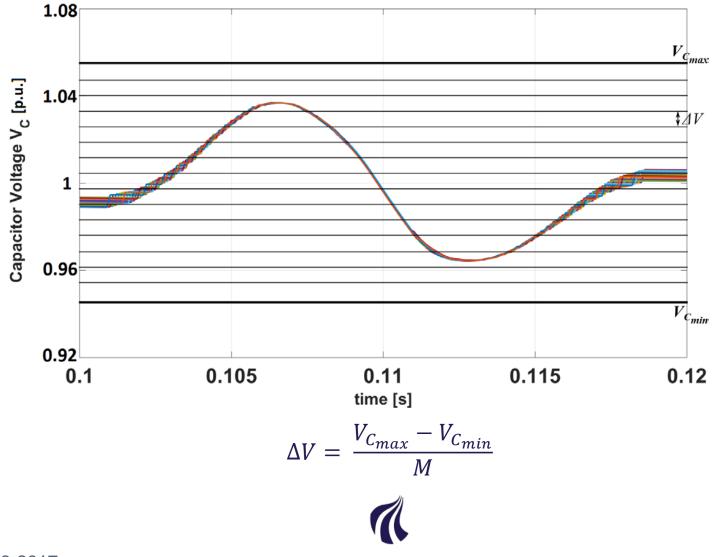

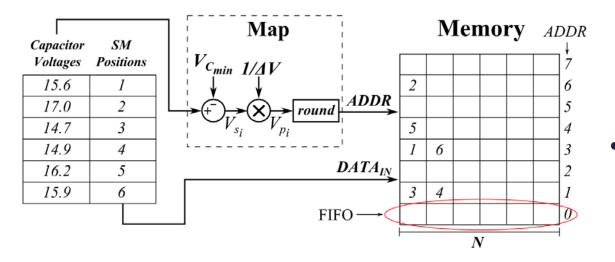

$$V_{C_{min}} = 14 V$$

$$\Delta V = 0.5 V$$

Inside a voltage range the capacitor voltage values are considered to be identical

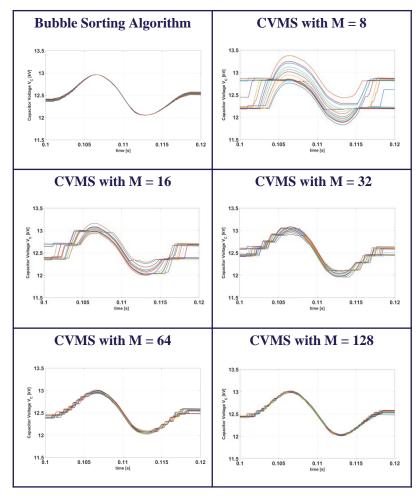

### **Simulation Results**

#### **Table: MMC parameters**

| Parameter                                              | Value  |

|--------------------------------------------------------|--------|

| <b>DC-link Voltage</b> V <sub>DC</sub>                 | 200 kV |

| SM Capacitor C                                         | 36 µF  |

| <b>Arm Inductance</b> <i>L</i> <sub><i>arm</i></sub>   | 50 mH  |

| <b>Arm Resistance</b> <i>Rarm</i>                      | 1 Ω    |

| Number of SM N                                         | 16     |

| <b>Sampling frequency</b> <i>f</i> <sub><i>s</i></sub> | 10 kHz |

#### **Table: grid parameters**

| Parameter                                       | Value    |

|-------------------------------------------------|----------|

| <b>Grid frequency</b> <i>f</i> <sub>grid</sub>  | 50 Hz    |

| Grid Voltage V <sub>grid</sub>                  | 121.2 kV |

| <b>Grid Inductance</b> <i>L</i> <sub>grid</sub> | 16.7 mH  |

| Grid Resistance R <sub>grid</sub>               | 0.52 Ω   |

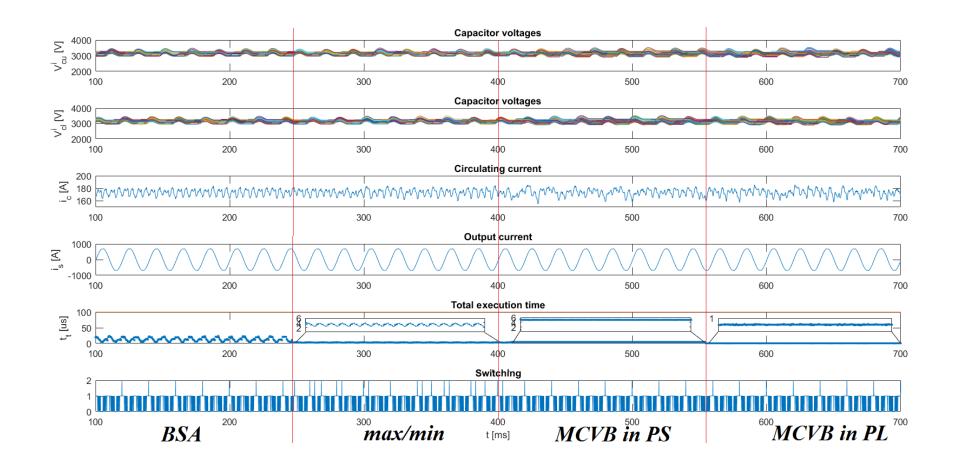

### **HIL Results**

#### >Introduction

Sorting Methods for NLCProposed Solutions:

- Sorting Networks

- Capacitor Voltage Mapping Strategy

- Two solutions have been proposed for the capacitor voltage balancing algorithm:

- Sorting Networks

- Capacitor Voltage Mapping Strategy

- The simulation results for the CVMS have been shown.

- $\succ$  The HIL results have also been presented.

# Thank you for your Attention

E-mail: mri@et.aau.dk